Conocidos comúnmente como Bloque Lógico Configurable, (Configurable Logic Block, CLB), estos bloques son la parte lógica mayoritaria dentro de un FPGA. Su estructura macroscópica se detalla en la Figura 1, donde se puede ver que un CLB está constituido por 4 rebanadas (Slices), SLICEM S0, SLICEM S1, SLICEL S2 y SLICEL S3, rutas de conexión para el acarreo matemático, Cin y Cout (carry in, carry out), conexiones a la matriz de conexiones (Switch Matrix) que proveen acceso a las rutas de conexiones generales y conexiones locales entre las rebanadas del mismo CLB y CLBs vecinos.

Figura 1. Esquema de un CLB y su conexióna la matriz de conexión

Tal como se aprecia en Figura 1 los SLICES se individualizan en coordenadas, desde al más abajo a la izquierda como SLICE X0Y0, hasta el superior derecho identificado como SLICE X1Y1. Del mismo modo para el CLB. Cada CLB se identifica con coordinadas XY dentro del arreglo matricial. Donde XY igual a 00 identifica el primer CLB en la esquina inferior izquierda de la matriz de CLBs, la coordenada del CLB suprior derecho dependerá del tamaño de la matriz, es decir del tamaño del FPGA.

1.1. Rebanadas (SLICE) de un CLB

Hay dos tipos de rebanadas (SLICEs) dentro de un CLB:

SLICEM: además de las funciones lógicas que se pueden implementar en el SLICE, ofrece opciones para implementar pequeñas memorias.

SLICEL: solo puede implementar funciones lógicas.

Figura 2. Vista simplificada de un SLICEL de un FPGA Spartan/ FPGAVirtex

La Figura 2 muestra una vista simplificada de un SLICEL, en la que se destaca lo siguiente:

- Dos tablas de búsquedas (Look-Up Tables)

- Dos flip-flops

- Cuatro salidas, dos combinacionales y dos con registros

- Tiene entradas de control para los flip-flops

- Entradas para las LUTs

- Entrada y salida para la cadena de acarreo (Carry Chain)

1.2. Tablas de Búsqueda - Look-up Tables (LUTs)

En un FPGA toda la lógica combinacional se implementa utilizando tablas de búsqueda, LUT, es decir la función lógica se almacena en una tabla de verdad de 16x1 (para las LUTs de 4 entradas). En cierta literatura a las LUTs también se les llama “Generadores de Funciones” (Function Generators). La Figura 3 detalla la similitud entre una tabla de verdad y una LUT. La columna de valores Z, valores de la función combinacional, son los valores que realmente se almacenan en la LUT de 16x1. Vale recordar que, a menos que por alguna razón se quiera hacerlo manualmente, el almacenamiento de los valores en las LUTs lo realiza el Software del fabricante del FPGA, siendo el proceso totalmente transparente al diseñador del sistema digital.

Figura 3. Cómo se implementa una función combinacional en una LUT.

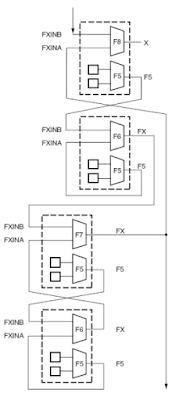

Una característica que a veces es de mucha utilidad, sobre todo para sistemas de muy alta frecuencia, es que el retardo a través de la LUT es constante e independiente de la función implementada. Para implementar funciones lógicas de más de cuatro entradas en una LUT, se usan multiplexores dedicados que están distribuidos en el SLICE(L/M) y en el CLB para poder implementar cualquier función con un mayor número de entradas. Por ejemplo, para implementar cualquier función lógica de cinco entradas se usa el multiplexer F5Mux, que multiplexa las salidas de las dos LUTs (4 entradas) y la quinta entrada funciona como señal de selección del F5Mux. Si bien estos multiplexores dedicados podrían ser implementados en las LUTs, al ser dedicados son más eficientes y dejan las LUTs disponibles para otras funciones. Estos multiplexores no se pueden ver en la Figura 2, al ser una vista simplificada de un SLICE. Pero sí se pueden ver en la Figura 4, donde se destacan

los siguientes multiplexores:

- F5Mux: multiplexa las salidas de las LUTs dentro del SLICE

- F6Mux: multpilexa las salidas de los F5Mux de un SLICE

- F7Mux: multiplexa las salidas de los F6Mux de un CLB

- F8Mux: multiplexa las salidas de los F7Mux de dos CLBs

Figura 4. Multiplexores dedicados y sus conexiones dentro de un CLB.

Como se puede ver en la Figura 4, cada SLICE tiene un F5Mux, y un segundo multiplexor llamado genéricamente FiMux. Esto se debe a que este multiplexor puede funcionar como F6Mux, F7Mux o F8Mux dependiendo de su ubicación y su conexión con los otros multiplexores. Se destaca que las conexiones entre los multiplexores se hacen a través de rutas de conexiones dedicadas a tal fin, con retardo cero. De todos modos, las salidas de estos multiplexores también están disponibles en la salida combinacional del CLB para acceder a las conexiones de ruteo general.

Nota: en la última versión de Spartan y Virtex, versión 6, las LUTs son de 6 entradas. Esto fue implementado después de trabajos de investigación llevados a cabo por Xilinx tratando de encontrar cual era el número óptimo de entradas para las LUTs. De todos modos, todo lo explicado en este punto para LUTs de 4 entradas, se aplica también para LUTs de 6 entradas.

1.3. Elementos de Almacenamiento. Flip-Flops

Figura 5. Detalle de la lógica del Registro/Cerrojo en un SLICE

La Figura 5 detalla las posibles configuraciones del elemento de almacenamiento y sus respectivas señales de control. Cada SLICE posee dos elementos de almacenamiento programables que pueden funcionar como flip-flop D, o cerrojo (latch) transparente. El elemento de almacenamiento ubicado en la parte superior del SLICE se denomina FFY, mientras que el de la parte inferior se denomina FFX. Ambos elementos de almacenamiento tienen un multiplexor de selección para la entrada D, pudiendo seleccionar entre la salida de la respectiva LUT, DY o DX, o una entrada externa al SLICE, llamada BY para el elemento FFY y BX para el FFX.

Se observa también que las señales de reloj, habilitación del reloj y reset (limpiar) son comunes al par de flip-flops en cada SLICE. El flip-flop tiene construido en su lógica interna la opción de poder poner en cero (reset) el flip-flop de manera sincrónica o asincrónica. La entrada REV (reverse) se usa

cuando se desea invertir el valor lógico de activación de la señal de reset.

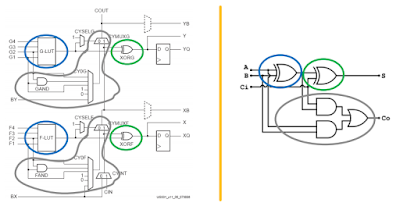

1.4. Lógica de Acarreo (Carry)

El CLB tiene lógica dedicada exclusivamente para el acarreo de la suma aritmética con el objeto de mejorar el rendimiento de sumadores, contadores, comparadores y funciones lógicas relacionadas. En la Figura 6 se detalla la lógica, descrita en compuertas, de cada bit de un sumador total. Mientras que la Figura 7 muestra la analogía entre la lógica del sumador total y la lógica disponible en un SLICE para implementar el sumador total de una manera más eficiente que si fuera implementado solo con LUTs.

Figura 6. Detalle de la lógica del Registro/Cerrojo en un SLICE

Figura 7. Relación entre la lógica de acarreo en un SLICE y el sumador total

La lógica de acarreo disponible en los CLB está constituida por los siguientes elementos, detallados en la Figura 7:

- Compuertas lógicas dedicadas sólo para el acarreo

- Multiplexores dedicados

- Ruteo y conexiones dedicadas

1.5. Componentes del SLICE

Después de haber visto en detalle los distintos componentes de un SLICE, es hora de ver como se utilizan e interconectan dentro del mismo. La Figura 8 muestra una vista generalizada de los componentes sin sus interconexiones.

Figura 8. Componentes de un SLICEM y SLICEL, sin sus interconexiones

Como ya de detalló en 1.1, los FPGA de Xilinx tienen los SLICELs y los SLICEMs. Tal como se ve en la parte izquierda de la Figura 8, el SLICEM permite implementar bloques de memoria, registros de desplazamiento y lógica combinacional en una especie de LUT-multifunción. En los dispositivos actuales, aproximadamente un 50% del total de los CLBs de un FPGA contienen SLICEM y el otro 50% SLICEL. En versiones anteriores de FPGAs, el 100% de los CLBs eran SLICEM, pero esto fue cambiando hasta llegar a la relación actual de 50-50. Esto se debe principalmente a dos motivos: primero, si bien el SLICEM es más genérico, físicamente ocupa más lugar que el SLICEL y por ende,

hace el dispositivo más costoso. Segundo, se llevaron a cabo intensos estudios del uso del CLB, y rara vez se usaba más del 50% de ellos como SLICEM.

La Figura 9 muestra todos los bloques vistos anteriormente por separado (excepto las funciones unidas por líneas de puntos que no se han descripto todavía), ahora juntos en un SLICEM. Se procederá a describir la mitad inferior del SLICE (que es exactamente igual a la mitad superior).

Figura 9. Detalle de un SLICEM

Cuatro líneas de señal de entradas, F(4:1), entran directamente a la LUT o Generador de Funciones F. Tal como se detalló antes, en la LUT o GF se genera la lógica combinacional necesaria. La salida de la LUT o GF, llamada D, tiene cuatro caminos posibles:

- Salir en forma directa o negada (XORF) por la salida X, pasando por el multiplexor FXMUX.

- Entrar por la entrada de datos D al elemento de almacenamiento FFX, cuya salida es XQ.

- Controlar el mutliplexor CYMUXF de la cadena de acarreo.

- Entrada de datos al multiplexor F5Mux para implementar funciones combinacionales de más de 4 entradas.

Otras entradas al SLICE son BY y BX, conocidas como Bypass Y y Bypass X. Estas pueden tener una de las siguientes funciones:

- Eludir (bypass) la LUT y entrar a la entrada D del elemento de almacenamiento. De este modo, en una mitad de un SLICE se puede tener al mismo tiempo una función combinacional y otra secuencial.

- Controlar el multiplexor F5Mux.

- Entrar a la cadena de acarreo.

- BY (solamente) controla la entrada REV de FFY y FFX (ver la Figura 5).