2. Bloque de Entrada/Salida (Input/Output Block, IOB)

Para poder recibir y transmitir señales digitales, los FPGAs disponen de un bloque de E/S bastante elaborado que posibilita usarlos con muy diversos rangos de tensiones, frecuencias de trabajo, estándares de señales digitales, etc, lo que los hace muy adaptables a las necesidades del sistema del que forman parte.

Existe un bloque E/S por cada terminal de E/S del FPGA. Así cada terminal puede ser configurado como entrada, como salida o bidireccional. En cada bloque E/S existe un buffer que tiene diversas funciones configurables por el diseñador que permiten adaptar el FPGA en un sistema complejo trabajando con diferentes tensiones y corrientes, en un circuito impreso con muchos problemas de integridad de señal (signal integrity).

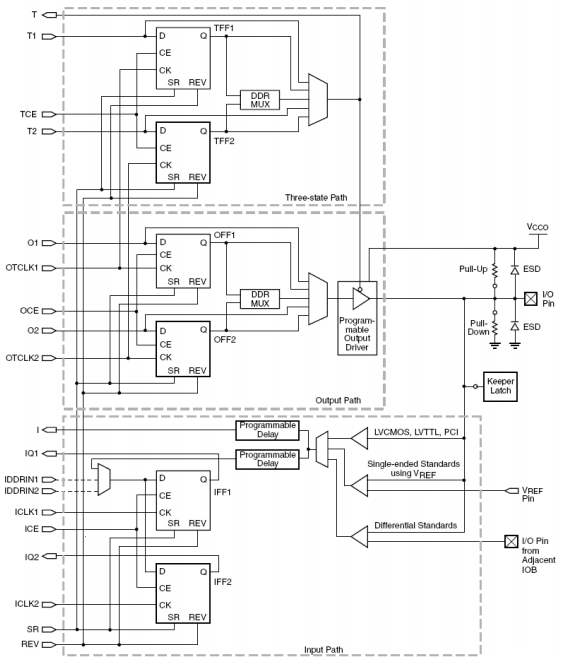

Figura 1. IOB de un Xilinx Spartan FPGA

a) Camino de entrada, que conecta el IO Pad (terminal del circuito integrado) a la lógica interna del FPGA. Esta conexión puede ser:

- Directa, a través de un elemento de retardo (opcional).

- Con registro usando el flip-flop IFF1

- Con registro usando el flip-flop IFF2

Las tres salidas del IOB, I, IQ1 e IQ2, se conectan al ruteo general interno del FPGA. El par de flip-flops IFF1 e IFF2 se usan para interfaces tipo DDR (dual data rate). De modo que el dato de entrada sea capturado en ambos flancos con distintos flip-flops. El flip-flop IFF1 suele ser usado como registro de entrada para reducir al mínimo el tiempo de establecimiento de la señal de entrada. Se observa también que cada entrada tiene un par equivalente (IO Pin from adjacent IOB) para el caso que se utilice una configuración de entrada diferencial, tales como LVDS.

b) Camino de salida, comunica la lógica interna con el IO Pad del FPGA. Entra al IOB por medio de O1 u O2, pasa a través de un multiplexor y del buffer de salida llegando al IO Pad. El par de flip-flops OFF1 y OFF2 se usan para transmitir datos en ambos flancos del reloj (DDR). También estos flip-flops se usan para poner registros en las señales de salida del FPGA, de modo de reducir al mínimo el tiempo de retardo de flip-flop (Clock to Output, Tco). Además, si se usan los IOB flip-flops en todas las señales de salida de un sistema, se reducen los diferentes tiempos de propagación entre las distintas salidas, generando una transición de las salidas “casi” al mismo tiempo.

c) Camino de alta impedancia, comunica la señal de control de alta impedancia con el buffer de salida. Esta ruta también dispone de un par de flip-flops para interfaces tipo DDR o para registrar en este bloque la señal de control de alta impedancia. Se observa también una realimentación de la señal que controla la alta impedancia del buffer de salida.

2.1. Buffer de E/S

El buffer de Entrada/Salida del IOB es un buffer configurable de acuerdo al estándar de la Entrada/Salida que se desea. La Tabla 2 detalla los diferentes estándares de E/S disponibles en un FPGA, con sus respectivas tensiones de entrada y de salida, como así también, si se necesita alguna tensión de referencia o de terminación.

En el caso del buffer de entrada, se puede configurar para trabajar con cualquiera de los estándares de E/S detallados en la Tabla 1. En algunos de estos estándares el buffer de entrada utiliza una tensión de referencia o disparo (threshold), VREF, que se suministra por un terminal determinado del FPGA. VREF normalmente se usa para generar las tensiones de referencia de estándares como diferencial HSTL (High Speed Transceiver Logic) y SSTL (Stub Series Terminal Logic). Este ultimo usado en las interfaces de memorias tipo DDR y DDR2.

En el caso del buffer de salida, también se puede configurar para un amplio rango de estándares de E/S, tal como detalla Tabla 1. Pero también se puede configurar su corriente de salida (drive strength) y la pendiente de la señal de salida (slew control). Con estos dos controles se pueden minimizar los efectos de rebote de señal (ringing) y las emisiones de alta frecuencia.

Tabla 1. Estándares de E/S soportados por el Bloque E/S (IOB)

Se puede observar en la Figura 1 que cada IOB tiene un diodo de protección a Vcco y otro a GND. Dispone de resistencias tipo pull-up y pull-down configurables, como así también un circuito de retención de bus (bus keeper o bus holder).2.2. Bancos de E/S

Los bloques de E/S (IOBs) están agrupados en lo que se llaman bancos de bloques de E/S (grupos de IOBs). Dependiendo del FPGA, cada banco puede tener entre 20 y 40 IOBs. Cada banco de IOBs tiene su propia tensión de alimentación (VCCO) y su propia tensión de referencia VREF que son comunes a todos los IOBs. Es por esta disposición de tensiones de VCCO y VREF por banco, que si se quieren usar diferentes estándares de E/S con diferente VCCO, se deberán usar diferentes bancos de E/S.

La Figura 2 muestra la división de los IOBs en 8 bancos de E/S en un FPGA Virtex 2.

Las herramientas usadas cuando se implementa un diseño en un FPGA automáticamente asignan terminales de diferentes bancos cuando los estándares E/S usados necesitan diferentes VCCO o VREF. De todos modos, el diseñador también tiene control suficiente para asignar terminales específicos de E/S a señales específicas de su diseño.

Otra característica disponible en los IOBs es la de control digital de impedancia (no representada en la Figura 1), que permite controlar la impedancia de entrada o la de salida de los terminales del IOB. Una aplicación típica es, por ejemplo, adecuar la impedancia de salida del FPGA a la impedancia de la traza del circuito impreso (típicamente 50 ohms), para evitar o reducir al mínimo las posibles reflexiones de la señal digital. Esta función es configurable en un esquema banco por banco de IO, es decir cada banco puede tener su propia adaptación de impedancia.

No hay comentarios:

Publicar un comentario