6. Generación de Reloj y su Distribución

Los FPGA tienen unos bloques de lógica dedicados exclusivamente a funciones de control y generación de señales de reloj. En los FPGAs de Xilinx a estos bloques genéricamente se los llama Digital Clock Managers (DCMs) (Gestores de Reloj Digitales). La cantidad de estos bloques disponibles en un FPGA depende del tamaño del mismo, puede haber desde 2 DCMs en los FPGAs más pequeños hasta 12 DCMs en los FPGA grandes.

Los DCMs integran capacidades avanzadas del reloj, dentro de la red de distribución dedicada del reloj del FPGA. Las principales funciones del DCM se pueden resumir en:

- Eliminar el sesgo del reloj (clock skew), ya sea dentro del FPGA o con componentes externos. De este modo se mejora el rendimiento del sistema y se eliminan los retardos de ruteo del reloj.

- Producir corrimiento de fase (Phase shifting) de una señal de reloj, ya sea por una fracción del periodo de reloj o por incrementos fijos.

- Multiplicar o dividir la frecuencia de entrada del reloj, generando una frecuencia completamente nueva.

- Acondicionar la señal de entrada del reloj, asegurando un reloj limpio, con un ciclo de trabajo del 50%.

- Amplificar de nuevo (rebuffer) una señal de reloj, normalmente para eliminar el sesgo (deskew) y convertir la señal de entrada a un estándar diferente, por ejemplo, de LVDS a LVTTL.

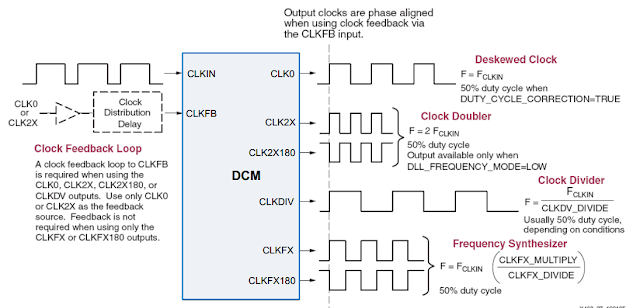

La Figura 1 detalla gráficamente las distintas funcionalidades del DCM explicadas en los puntos anteriores (excepto el corrimiento de fase).

Figura 1. Diferentes opciones de uso del DCM

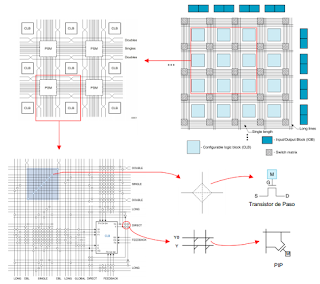

Tal como se explicó anteriormente, la señal de reloj usa rutas de conexión dedicadas, cuya distribución dentro del FPGA es bastante particular, tal como se puede ver en la Figura 2. El FPGA se divide en cuatro cuadrantes, los cuales pueden tener como máximo 8 relojes. Multiplexers dedicados seleccionan las señales de reloj que se van a usar en cada cuadrante. Las líneas de ruteo de reloj son líneas dedicadas de muy bajo retardo, de casi nula distorsión del ciclo de trabajo, con jitter (oscilación) mínimo y llegan a todos los elementos sincrónicos del FPGA.

Figura 2. Distribución de los DCMs y rutas de reloj en un FPGA Spartan

Los buffers de entrada (A-H) son buffers con características especiales, como, por ejemplo, conexión directa con el DCM (para evitar retardos de ruteo). De todos modos, una señal de reloj externa puede entrar a través del buffer de entrada y ser ruteado a los flip-flops del FPGA sin pasar por el DCM.

Para configurar un DCM se usa un software del fabricante del FPGA. En el caso de Xilinx se llama CoreGen (Core Generator) el cual tiene una interfaz grafica que facilita la configuración del DCM de acuerdo a las necesidades del diseño.

6.1. Ejemplo de uso del DCM- Eliminando el sesgo del reloj

Se detallará un ejemplo de uso del DCM como supresor del sesgo del reloj del sistema.

En todo sistema sincrónico existe inherentemente sesgo de reloj. Aún la señal de reloj más precisa llega en tiempos diferentes a los diferentes puntos del sistema, ya sea en un mismo dispositivo o a los diferentes dispositivos conectados a la fuente de reloj. Esa diferencia en el tiempo de llegada se conoce como sesgo de reloj (clock skew).

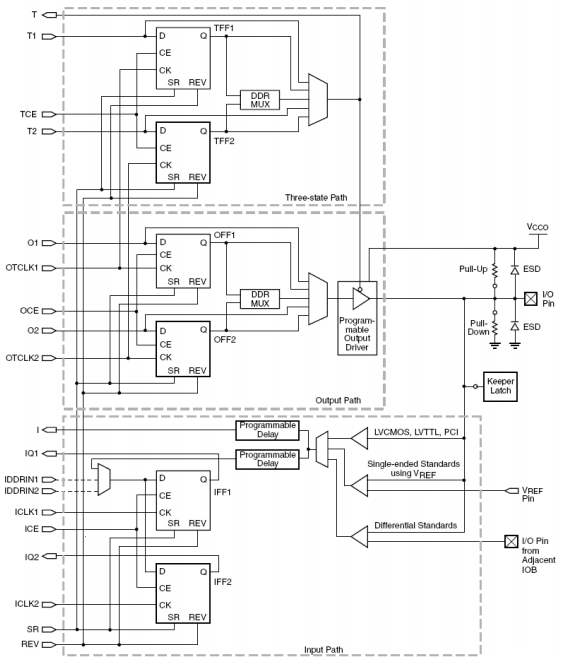

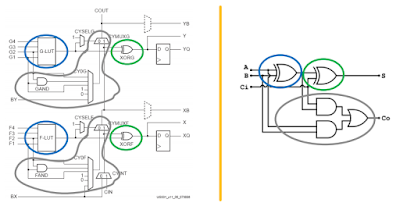

La Figura 3 detalla un ejemplo de un sistema simple que consta de un FPGA y otro dispositivo, que puede ser, por ejemplo, un microcontrolador, un ASIC, o lógica discreta. El reloj entra al FPGA (punto A) a través de un buffer de entrada, por ende sufre un cierto retardo. Usando ruteo dedicado (mínimo retardo, pero retardo al fin) llega a los flip-flops del FPGA (punto B). Luego de un cierto retardo, llamado ∆b en la Figura 3, sale a través de un buffer de salida (más retardo). Además, se le debería sumar también el retardo que sufre la señal a través de la línea de conexión del circuito impreso. Así, cuando el reloj llega al otro dispositivo (punto C) tiene un cierto retardo, creando un cierto desfasaje (sesgo) con el reloj original y con el reloj interno del FPGA (llamado ∆C en la Figura 3). El retardo es tal, que si se quieren transmitir datos desde el FPGA al dispositivo (punto D) se corre el riesgo de violar los tiempos del establecimiento o sostenimiento en el flip-flop del dispositivo receptor.

Figura 3. Sistema con sesgo de reloj

Este problema del sesgo del reloj en la jerga técnica se conoce como "el ladrón del rendimiento del sistema". Como consecuencia de todos estos retardos, se incrementan los tiempos de establecimientos y los tiempos de retardo de los flip-flops (clock to output) y por lo tanto, se incrementa el periodo de reloj del sistema. De forma análoga, en algunos casos también puede que se requieran tiempos de mantenimiento más largos. Todos esto lleva a que necesariamente se deba buscar una solución a este problema.

Afortunadamente los DCMs internos de un FPGA ofrecen una manera sencilla de eliminar el sesgo de reloj de un sistema. La Figura 4 muestra un ejemplo de uso de dos DCMs del FPGA, un DCM tiene como función eliminar el sesgo del reloj dentro del FPGA, y el otro DCM elimina al sesgo del sistema, resultando prácticamente un alineamiento ideal del reloj en los distintos puntos (A, B, C, D) del sistema.

Figura 4. Uso de DCMs para eliminar sesgo de reloj dentro del FPGA y del sistema

¿Cómo se elimina el sesgo del reloj?. Se debe recordar primero que el sesgo es provocado por los retardos en el camino del reloj (buffers, ruteo, etc). En la Figura 4 el reloj en el punto B está retardado por ∆B y el reloj en el punto C está retardado por ∆C. Qué pasaría si existiera un modo de proveer en el punto B una versión ‘adelantada’ por el tiempo ∆B del reloj?, y otro modo de proveer al punto C una versión ‘adelantada’ por un tiempo ∆C del reloj? El resultado sería que todos los relojes arribarían a su destino perfectamente alineados tal como muestran las formas de ondas de la Figura 4-B. En realidad, el DCM lo que hace es retardar la señal de entrada de modo que parece estar adelantada en el tiempo. Por ejemplo en la Figura 4-C, el reloj en el punto B parece estar adelantado en el tiempo por el retardo ∆B. Sin embargo, la realidad es que el reloj está retardado por T (periodo del reloj)- ∆B. Del mismo modo para el reloj en punto C, el cual es retardado por T-∆C.

Una ventaja aún mayor al usar el DCM es que no es necesario conocer los valores de ∆B y ∆C, es decir no hace falta ni calcularlos ni medirlos, sino que el mismo DLL dentro del DCM constantemente monitorea el retardo por medio del lazo de realimentación (feedback loop) tal como se muestra en la Figura 4-A. Al usar los DCMs la performance total del sistema es óptima, anulando cualquier inherencia del sesgo del reloj en la misma.