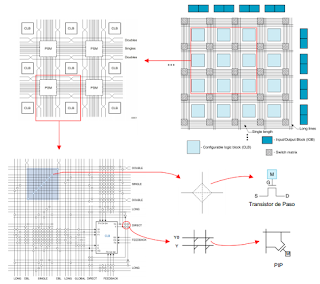

Además de las celdas de lógica programable, los FPGAs tienen celdas de interconexión programables. Estas definen el camino (ruta) a seguir por cada señal interna del FPGA. La tecnológica de configuración y la arquitectura de la celda lógica determinan la estructura y complejidad de la interconexión. La Figura 1 muestra cómo se distribuyen las rutas de interconexión entre los CLBs. A la izquierda se muestra más en detalle cómo es la conexión interna entre las diferentes rutas de conexión, programable a través de transistores,

Figura 1. Interconexión entre distintos caminos de ruteo

La programabilidad de la interconexión, si bien es una gran ventaja, agrega retardos a la señal que pasa por el transistor. Así, si una señal debe pasar por varios elementos de interconexión la suma total de los retardos puede ser considerable y debe ser tenida en cuenta en diseños de alta frecuencia. Por ello, a fin de no ir sumando demasiados retardos en cada interconexión, existe lo que se llaman rutas largas. De este modo, si una señal tiene que pasar por más de medio dispositivo puede hacerlo usando estas rutas largas, evitando las interconexiones intermedias. Del mismo modo, existen también las rutas cortas, llamadas conexiones directas, que comunican un bloque lógico con sus bloques vecinos.

Dentro del FPGA también existen lo que se llaman rutas dedicadas, que se usan para las señales que tienen mucha cargabilidad de salida (fan-out) en el sistema que se está diseñando. Las señales que más comúnmente usan las rutas dedicadas son el reloj y la habilitación del reloj (clock enable). Estas rutas tienen buffers especiales que hacen que la señal no se distorsione con la carga. Por ejemplo, en diseños grandes es fácil encontrar una señal de reloj que llegue a 2000 flip-flops.

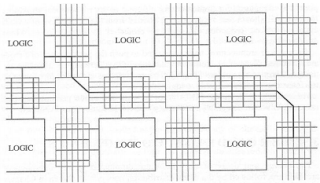

Hay una relación directa entre la cantidad de interconexiones y el tamaño físico del FPGA. Por ello es que no se implementan físicamente todas las interconexiones posibles, así como, no todos los bloques lógicos están interconectados entre sí. A raíz de esto, para poder conectar la salida de un bloque lógico con la entrada de otro a veces se pasa por diversas interconexiones que conectan diferentes rutas para poder llegar a destino. Por suerte para el diseñador, el software del fabricante del FPGA realiza automáticamente todas las interconexiones. Es una tarea totalmente transparente al diseñador, siempre y cuando se cumplan los requisitos de tiempo estipulados por las especificaciones del sistema implementado. De lo contrario, el diseñador deberá optimizar algunos parámetros de la herramienta de ruteo (llamada Place and Route) para que pueda cumplir con las especificaciones de tiempo requeridas.

Figura 2. Vista macroscópica a vista microscópica de las interconexiones de un FPGA de Xilinx

La Figura 2 detalla las interconexiones en un FPGA de Xilinx. Se destacan las líneas verticales y horizontales que corren entres los bloques lógicos. La matriz de interconexiones programable (Programmable Switching Matrix, PSM) conecta las diferentes rutas dentro del FPGA a través de los transistores de paso. Se observan también las rutas largas (long lines) que cruzan todo el FPGA. Las rutas de conexión directa saltan sobre las matrices de interconexión para conectar directamente bloques lógicos adyacentes. Se destacan también los transistores que conectan las entadas y salidas de los bloques lógicos a las rutas generales de interconexiones, llamados puntos de interconexión programables (Programmable Interconnection Points, PIP). La Figura 3 detalla cómo se conectan dos bloques lógicos por medio de las matrices de conexión programables (PSM) y los puntos de interconexión programables (PIP).

Figura 3. Ejemplo de ruteo entre dos bloques lógicos a través de PIPs y PSMs

Finalmente, la Figura 4 resalta la importancia de las interconexiones de ruteo en un diseño. Es decir, del total de los recursos de un FPGA usados en este diseño, el 31% corresponde a recursos de interconexión, que es el porcentaje más elevado de recursos usados en este caso. Es por ello que este tema de las interconexiones y el ruteo son de gran importancia, realizándose estudios complejos para obtener algoritmos de optimización del ruteo, a fin de obtener resultados óptimos y evitar el congestionamiento de las rutas de conexión que derivan en una reducción del rendimiento general del FPGA.

No hay comentarios:

Publicar un comentario